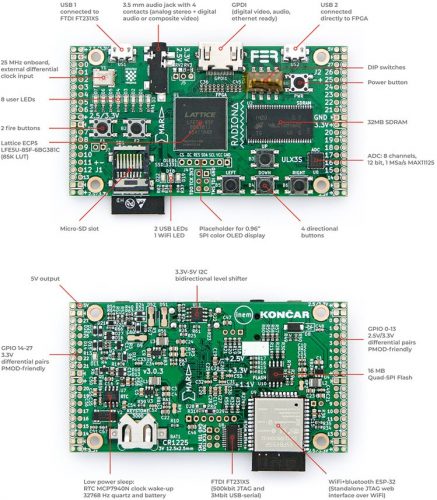

ULX3S is a fully open source, compact, robust, and affordable FPGA dev board equipped with a balanced selection of additional components and expansions. Although it was designed primarily as a teaching tool for mastering the principles of digital circuit design, ULX3S incorporates a wide array of features and interfaces that allow it to serve as a broadly useful module for installation in complex devices.

Built around a powerful Lattice Semiconductor ECP5-series FPGA chip and supported by the latest open-source toolchains, ULX3S is one of the most powerful and desirable platforms available for FPGA enthusiasts. It comes equipped with onboard Wi-Fi, display, buttons, LEDs, and storage. Flash it with an over-the-air (OTA) update using the Wi-Fi connection or take advantage of the onboard OLED display and buttons to browse the contents of an SD card and select a bitstream. Due to its battery-backed RTC, ULX3S can power down completely and wake up only in response to certain events. This feature makes it perfect for use in low-power applications such as battery-powered remote sensor nodes.

And if you’re not the low-power type, onboard peripherals like SDRAM, USB, digital video out, onboard FM/ASK antenna, ADC, and DAC make it an audio/video powerhouse for signal processing and synthesis, motor control, and SDR use cases. It can emulate arcade machines and retro computers like the Minimig (Amiga) or modern systems like the F32C (MIPS/RISCV). It has 56 GPIO pins, all routed as differential pairs, and a PMOD compatible pinout, which opens it up to a wide range of expansion options. And if you are just starting out FPGAs, you can use the Arduino IDE to program ULX3S in seconds.