Open architectures for processors too? It looks like it can be done, and probably in the near future.

The project of an “open hardware” CPU, entertained only in the academic work until now, is now ripe for commercial purposes. At FOSDEM in Brussels (international conference on open-source projects), which took place in February 2018, we have attended the presentation of the first board equipped with Linux-ready, 64-bit RISC-V CPU. The mission of RISC-V is to “democratize” the access to silicone, in order to give startups, universities and even single individuals the possibility to design and implement their own CPU on discrete logic or FPGA, without having to pay the excess costs due to royalties and with the total documentary visibility of the project.

Not only that, but the RISC-V Foundation has been thought out to be “democratic”: any evolution must be subject to discussion and approved after a consensus and obtained based on purely technical reasons, not on patent wars, nor the necessity to force obsolescence for commercial purposes. Everyone can subscribe to the RISC-V Foundation: both private individuals and companies.

In order to better understand what the RISC-V is all about, let’s start from the beginning.

What is RISC-V?

It is an ISA (Instruction Set Architecture) hardware architecture of the RISC type, developed by the Berkeley University since 2010. The ISA is the instructions set acting as an interface towards the CPU hardware, composed of memory (and registers) and logic ports (executing the calculations between the registers). In other words, the ISA describes the syntax of the “machine language”, which is the instruction set the CPU is capable of carrying out. In order to make life a little easier for programmers, each ISA instruction (which is actually a number, typically a 32-bit one) can be described through an Assembly mnemonic language. For instance, the following instruction:

add a0,a2,a4

Means ‘save the sum of the values contained in registers a2 and a4 in the register a0’. A program called “assembler” therefore translates the text string in the corresponding binary number.

The importance of knowing the CPU Assembly has become increasingly less relevant over the decades, with the rise of compiled languages (e.g. C/C++). However, there are numerous reasons and practical applications for which it is recommendable to know something about an ISA and the general principles of Assembly. RISC systems (Restricted Instruction Set Computing) are based on a limited and efficient instruction set. The basic idea is simplicity of instructions, which doesn’t mean lack of performances, but, on the other hand, it means being able to get the best possible result by keeping maximum project simplicity; in fact, RISC executes complex operations with a single instruction, therefore with only one clock cycle, unlike a traditional CPU requiring more instructions for the same task and therefore more clock cycles. In order to understand the importance of this approach nowadays, just keep in mind that the vast majority of smartphones currently on the market is based on ARM processors, which are ISA RISC.

The origins of RISC

A little history in order to understand how we came to RISC and RISC-V, which is the latest research and development frontier. An example of a non-RISC system is the Intel x86 architecture. Born in 1978 for the Intel 8086, it has evolved over the years up to the modern Intel Core i9 processors; in order to get better and better performances, new instruction sets have been added over the years, in an incremental manner. Some of you will remember the SSE extensions introduced by Intel in 1999 starting from the Pentium III processor; many others followed. The base idea of Intel was to have an incremental system, in which each new implementation necessarily had to support all the previous instruction set. This gave us the possibility to replace our personal computer over the years while maintaining the software. This approach, however, has a considerable disadvantage: possible inefficiencies and design errors or instructions which are almost never used in practice must always be implemented with consequences on the processor’s hardware resource consumption. Besides, complex instructions, executing more operations (in various clock cycles) with a single instruction, are hard to use and make the implementation of the hardware and software itself more difficult, as well as long-term maintenance of the project and its future evolutions. Besides, the Meltdown and Spectre bugs are drawing attention to the risks of such complex systems, in terms of security.

The RISC philosophy started to take traction at the beginning of the 80s and began to be commercially available starting from the 90s. Among the most successful CPUs, we remember the SPARC processor, the PowerPC, the MIPS and the ARM. All these processors share a similar philosophy:

- quick instructions thanks to the pipeline (see in that box);

- fixed width for instructions, typically 32 bit: this simplifies the design phase of the hardware tasked with interpreting instructions;

- a fast number of registers, to minimize RAM memory accesses;

- simple methods of memory addressing.

RISC-V uses all the concepts explained, along with the technical optimizations coming from experience, the project designers tried to take all the good ideas from pre-existing projects and fix their shortcomings. It aims to become a scalable standard, in order to be used by small microcontrollers with less RAM and low consumption, up to more performing 64-bit processors. The RISC-V is released under permissive, open source license: this means that anyone can implement a RISC-V architecture without having to pay any royalties, unlike what happens with commercial solutions (e.g. ARM). Besides, there are already some implementations of ISA in Verilog and VHDL available on the web; we particularly suggest, to whoever is interested, to keep an eye on the SiFive website (www.sifive.com), founded by the creators of RISC-V to market the project. The RISC-V’s ISA is available at https://riscv.org/specifications/. On a technical level, unlike the incremental approach mentioned above, RISC-V (which official logo is shown in Fig. 1) calls for a modular approach. There is a minimal instruction set, called RV32I, including all the instructions to execute memory accesses, jumps, branches and logical operations and additions/subtractions of integer numbers, which will never change and it is the only system compulsory defined by the standard.

Fig. 1

Therefore, any project designer who wants to implement a RISC-V shape will have to support RV32I, but he won’t be forced to implement anything else he doesn’t need. This makes RISC-V particularly fascinating for all those situations where you need an affordable, low consumption CPU, to only carry out the most basic operations.

All other characteristics of RISC-V are optional based on specific implementations; the most relevant are;

- RV32M: multiplication and division of integer numbers;

- RV32FD: operations on floating-point numbers (32 and 64 bit);

- RV32A: atomic operations;

- RV32V: vector operations;

- RV64: 64-bit instructions.

Without going too in-depth into the technical aspects, one thing we were particularly struck by is the elegance of some choices, one of which is also in the MIPS: there is a register called x0, which value is always 0. This reduces the instruction set. For instance, in order to provide the negation value of the content of register t0 in register t1, the hardware doesn’t need to support the neg operation; instead, you can see the negation number as subtraction between the two registers, in which the first register is x0. In other words:

sub t1,x0,t0

Means “t1 = 0 – t0 = – t0”. We also find the RV32V extension to be very interesting: it allows to simultaneously execute operations on generic type vectors, by using, after an initial configuration, the same instructions regardless of the type (integer, floating-point). This also contributes to a certain elegance and to minimize the instruction set, besides being vital in all those applications requiring calculations on vectors and matrixes (e.g. FFT). For those of you wishing to find out more, from a technical perspective, we recommend the book The RISC-V Reader (Fig. 2): the fact that a book of just 160 pages manages to comprehensively describe the entire architecture is indicative of the diffusion potential.

Fig. 2

As for the software, the real news in the last months was the incorporation of RISC-V architecture in the main line of Linux kernel, starting with the 4.15 release: this, on one hand, guarantees a certain maturity of the Linux porting, and on the other hand, it allows all the current and future features of Linux to be automatically available for RISC-V as well. Besides, it shows that the toolchain gcc for Linux and the various tools and libraries (Binutils, libc etc) are stable enough to be actually used.

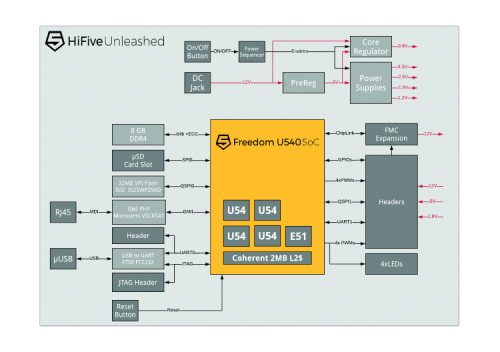

On the hardware side, SiFive produces the HiFive1 (an Arduino-like board) and they announced at FOSDEM the forthcoming production of HiFive Unleashed (Fig. 3 and Fig. 4), the first 64-bit, RISC-V development board on which you can run Linux. Still, on the SiFive website, you can download the bitstream for Arty FPGA Dev Kit (eight $99 board).

Fig. 3

At the moment, it is hard to predict what the future will be for RISC-V. There is definitely the hope this project will start to catch on in the academic world, in order to provide the students with an open system to study and train.

For commercial purposes, it would have to face stable and performing systems like ARM and MIPS, leading companies in the embedded market, which business is to resell their IP projects (Intellectual Property), underpayment of royalties, to companies which produce chips. However, for manufacturers (Texas Instruments, Qualcomm, NXP, ST etc.), The possible success of RISC-V, be it on widescale or for limited fields (e.g for IoT), would allow them to project their own SoC in absolute freedom without having to pay licenses. In our opinion, it is not a coincidence that names like Google, NXP, Nvidia, Qualcomm and Samsung are among the members of RISC-V foundation (https://riscv.org/members-at-a-glance/), among many other companies less known to the general public.

Fig. 4

We don’t want to talk too long about that since there is no sufficient visibility and knowledge of the marketing strategies of the various companies involved.

In conclusion, we think the real success of RISC-V will be measured by its technical performances (calculation speed, production costs, energy consumption), which are currently the real mystery, since there is no benchmark available to measure them. Once the first commercial products are available, we will be able to assess if the RISC-V architecture will keep its promises.

[…] To read more, please visit: https://www.open-electronics.org/risc-v-the-era-of-open-source-cpu-has-begun/. […]