SiFive announced the availability of the 64-bit, quad-core U54-MC Coreplex – the first Linux-ready application processor built around the open source RISC-V architecture. Fabricated with a TSMC’s 28nm HPC process, the real-time capable U54-MC Coreplex is the first multi-core RISC-V design, and the first to offer cache coherence. The processor is intended for AI, machine learning, networking, gateways and smart IoT devices.

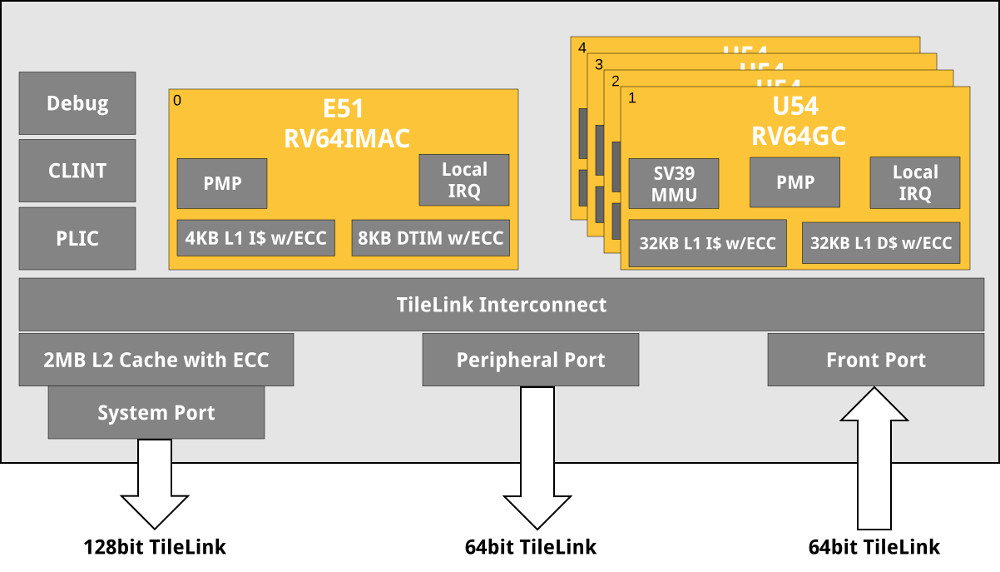

The U54-MC Coreplex combines four U54 cores and a E51 management core. The U54 cores support the RV64GC ISA which, according to SiFive, is expected to be the standard for Linux-based RISC-V devices. The U54 cores clock from between 960MHz to 1.5GHz, although there’s also mention of 1.7 DMIPS/MHz and 2.75 CoreMark/MHz performance.

There are no GPUs or other co-processors in the U54-MC Coreplex design, but its customizable nature will enable customers to add their own. SiFive will even work with customers to develop different core configurations aside from its current 4+1 design.Customers can built peripheral IP with an open source, native TileLink interface bus. This high-performance scalable cache-coherent fabric is available with bridge adapters for legacy bus protocols such as AXI4, AHB-Lite, and APB.

Aside from being open source and customizable, one of the main benefits of RISC-V is that it is fully modern, purpose built, and unburdened with legacy code. Over the last year, SiFive customers like Microsemi and Arduino have released various RISC-V based MCU chips. Just few months ago we spoke about it announcing the Arduino Cinque, board based on SiFive’s HiFive, featuring a RISC-V FE310 SoC and an ESP32 wireless module.

For further information take a look at the official Sifive’s announcement or watch the specs listed below.

• Fully compliant with the RISC-V ISA specification

• 4x RV64GC U54 Application Cores:

o 32KB L1 I-cache with ECC

o 32KB L1 D-cache with ECC

o 8 Region Physical Memory Protection

o 48 Local Interrupts per core

o Sv39 Virtual Memory support with 38 Physical Address bits

• 1x RV64IMAC E51 Monitor Core:

o 4KB L1 I-Cache with ECC

o 8KB DTIM with ECC

o 8 Region Physical Memory Protection

o 48 Local Interrupts

• Fully Coherent TileLink Bus

• Integrated 2MB L2 Cache with ECC

• Real-time capabilities:

o Both the L1 Instruction Cache and the L2 Cache can be configured into high speed deterministic SRAMs

• CLINT for multi-core timer and software interrupts

• PLIC with support for up to 511 interrupts with 7 priority levels

• Debug with instruction trace

• U54 Performance:

o 1.7 DMIPS/MHz

o 2.75 CoreMark/MHz