It allows to change the revolutions per minute in any brushed motor that is powered by 12 to 35 Vcc, thanks to a handful of electric components and to the popular 555 timer.

In different applications, such as for example electric drills and screwdrivers (and fans as well), it becomes necessary to adjust – by means of a manual control – the rotation speed of the electric motor’s shaft (that activates mandrels, blades, etc.). When it comes to AC motors, the technique of choice is the cutting phase, obtained by means of a dimmer that has a TRIAC as an output stage, but in the case of DC motors – and specifically the brushed ones – we need a method for varying the mean value of the voltage that is applied to the rotor windings; the most convenient choice is the one to prefer a circuit like the one proposed in these pages, that is a Pulse Width Modulator with a MOSFET power output. But before going into detail of the diagram that describes it, it is the case to spend some paragraphs so to explain why the PWM is the technique of choice for the control of the DC motors.

Let’s start from the point of view that the rotation speed of the DC motors depends on the voltage applied to the brushes, on the current drawn and on the load applied (load torque). The machine torque on the shaft is proportional to the current drawn. Therefore, in order to adjust the speed of such a motor, we need to vary the voltage that powers it and to supply the current of the case, when it is requested.

Why to choose PWM?

The most immediate solution would be the one to use a rheostat or a series voltage regulator, however that would have the consequence of dissipating too much energy, the mechanical power provided by the shaft being equal; in fact the rheostat is a resistor that makes a voltage (that is proportional to the current passing through it) drop at its ends, therefore as a first thing it has to dispose of the power under the form of heat, and it must therefore be consequently sized. It would not then be possible to keep a connection between the pointer’s position and the rotation speed, since an increase of the load on the shaft would determine an increase of the current drawn and therefore a decrease of the voltage applied to the brushes, that would imply a slowing down. In order to keep a connection between the pointer’s position and the rotation speed, it would be possible to use a potentiometer, by powering – by means of the voltage between the pointer and ground – a power DC amplifier, whose output powers the motor; in this case, however, there would still be the problem that the element regulating the voltage (the amplifier, in this example) would dissipate a power that is equal to the difference between the power voltage and the output voltage, the whole being multiplied by the current supplied to the motor.

We need therefore a solution that allows us to adjust the power supplied to the motor, but without losses or almost so; this solution is the Pulse Width Modulation, that consists in supplying rectangular pulses having a constant width (equal to the motor’s nominal voltage) to the motor, but with a variable width and still keeping the frequency constant at a value that is acceptable for the motor. It is therefore the case to vary, during the period, the ratio between the duration of the pulses and the absence of voltage, a ratio that is known as duty-cycle in the electric field, and that is expressed by the following formula:

dc = th/T

in which th is the duration of the pulse at a high level and T is the period, formed by the duration of the pulse and by the pause.

The established configuration of the Pulse Width Modulator, that is to say, of the circuit that generates pulses having a constant frequency but modulated as for the width, is based on a voltage comparator that receives a triangle wave as an input, while on the other one it receives a continuous component, that may be manually supplied by means of a common potentiometer, or automatically via a circuit or a microcontroller’s output; if we suppose to apply a direct voltage to the inverting input, we will see that when the potential of the rectangular wave exceeds the comparator, it generates the pulse at a high level as an output, while when it is lower, the output remains at a low level.

Circuit diagram

In these pages, however, we would like to propose a way to generate a rectangular signal in PWM that is a bit different, that is to say, we used the ever-present and versatile 555 timer in a slightly unusual configuration; in fact, by taking advantage of the functioning of the said integrated circuit in the astable configuration, and by making the duty-cycle vary, thanks to a gimmick that takes advantage of the different modes for loading and unloading of the timing capacitor (that in the circuit diagram found in these pages is the series of C1 and C2, at about 500 picofarad).

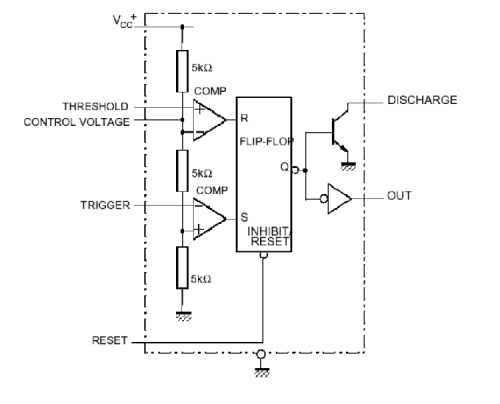

In order to let you understand the subject, we will spend a few paragraphs explaining the functioning of the 555 timer: this integrated circuit contains two comparators having a multiple voltage divider in common; the latter polarizes the inverting input for the upper operational amplifier and the non-inverting input for the lower operational amplifier. The non-inverting input of the upper one, corresponding to the pin 6 (THLD, that is to say, Threshold) and the inverting one of the upper one, corresponding to the pin 2 (TRG, that is to say, Trigger) of the comparators are made accessible from the outside (note that terms “upper” and “lower” are referred to the reference potential that they receive from the multiple voltage divider, therefore the upper one receives the highest voltage). The node between the first and the second (as considered from the point of view of the positive powering) resistors of the reference multiple voltage divider of the two comparators (that is powered, as the rest of the stages that are internal to the timer 555, by pin 8) is brought outwards by means of pin 5 (CTRL, Control Voltage) and this allows to alter the reference voltages of the comparators, so to control the operating frequency in the astable configuration (by operating the frequency shift as it is carried out in the VCOs, that is to say, the oscillators that are controlled in the voltage) by means of an external voltage, or to control the duration of the pulses in the one from the timer (monostable). More exactly, in the astable configuration, by lowering the voltage on pin 5 the output’s commutation period is shortened, and therefore the generated frequency is increased; vice versa, by letting the voltage increase up to the typical level (idly, that is to say, without any circuit connected to pin 5) or by increasing it, the period is increased and the generated frequency is reduced. On the other hand, in the monostable configuration the voltage alters the duration of the pulses, which allows – by driving the trigger with pulses having a constant frequency – to obtain a Pulse Width Modulator. One of the outputs of the comparators enters the RESET (the one of the upper comparator), the other one enters the SET (lower comparator) of a flip-flop of the RS type, that is a logic circuit whose direct output (Q) goes to high level (corresponding to about the potential of the pin 8) when the SET is at a high level, that is to say, when it takes on the value of logical zero if the SET is set to about zero volts; the output has a behaviour that is exactly the opposite one with respect to the case in which it is the RESET input to be excited; when set at a high logic level, the latter resets the flip-flop (in this way meaning that it zeroes Q’s state). The flip-flop also has a complemented output (/Q), whose logic condition is always the opposite one of Q; in the 555 timer it is connected – by means of a resistor – to the base of the NPN transistor, that is configured as an open collector whose emitter is connected to ground and the collector to the DCHR (Discharge, 7) pin. Used in the current absorbing mode, the transistor may commutate a collector current of 200 mA. The direct output, Q, is on the other hand connected to the OUT (3) pin of the integrated circuit by means of an internal push-pull buffer, that is capable of supplying a maximum of 200 mA. The power source’s negative, that is to say the 555 timer’s reference ground, corresponds to the pin 1, while at pin 4 the reset having the inverted logic of the flip-flop is connected: this pin allows to force reset the circuit from the outside, by applying a low logic level. The maximum operating frequency of the 555 timer, when configured as astable, is 500 kHz. This being said, it is possible to see that the 555 timer’s circuit is configured as astable, with a small modification to the canonical circuit, that considers a resistor between pins 4, 8 and 7, another one between pins 7 and 2, 6, and a capacitor between the latter ones and ground; in our case, the resistor between the pins 4, 8 and 7 (that we will name Ra) and the one between 7 and 2, 6 (that we will name Rb) may change, one at the disadvantage of the other one, thanks to the fact that in the middle there is a potentiometer whose pointer (that is connected to pin 7), may get near to R1 (thus reducing the resistance between 4, 8 and 7) or to R3 (thus reducing the resistance between 7 and 2, 6 and, as a consequence, the one between 4, 8 and 7 is increased). In order to let you understand what occurs, we will analyze – with reference to figure – the functioning of the circuit, starting from the unloaded C1 and C2 (and therefore having a voltage of 0 volt): we will omit the events concerning C3, that is almost immediately unloaded and therefore it does not bother the reference voltage applied by the multiple voltage divider to the comparators that are internal to the 555 timer; the initial condition of the circuit is the one with the pins 2 and 6 at about zero volts and therefore the lower comparator’s output is at a high level: this determines the logic high level on the SET input of the flip-flop and the same on the Q output (the /Q is brought to logic zero, thus leaving the transistor connected to the DISCHARGE interdicted, and therefore the capacitor is free to charge). At this stage, C1 and C2 start to charge by means of the current flowing through the series R1, R2, R3 (and also in the D1 diode that we will neglect at the moment; pin 7 does not absorb anything), until the threshold voltage of the lower comparator (that is equal to ⅓ of the one applied to the pin 8) is exceeded. Now, the output of the abovesaid comparator is brought to logic zero and it frees the flip-flop’s SET, whose output still remains at a high level until the voltage at the ends on C1 and C1 – that keeps growing – reaches a value above the ⅔ of the power voltage of the 555 timer, that is to say the commutation threshold of the upper comparator.

When this occurs, the upper comparator’s output is brought to a high logic level and it resets the flip-flop, whose direct output goes to logic zero while the /Q is brought to high level, thus sending the internal transistor to saturation; the latter is connected to the pin 7, that by means of R2 discharges C1/C2, but by means of R3 and of the potentiometer’s resistor, that is inserted between the end connected to R3 and the pointer, since D1 is now interdicted. This is the situation, as long as the voltage on C1 and C2 doesn’t go below the commutation threshold of the lower comparator, when the output of the latter returns to a high logic level and sets the flip-flop, that returns Q to logic 1 and /Q to zero. In this condition, the capacitor resumes charging since the pin 7 returns to the open state.

The charging occurs again until the 2/3 of the voltage applied between the 555 timer’s pins 1 and 8 is reached, after that the cycle restarts.

As a consequence of this, there is the OUT output of the integrated circuit that is kept at a high level during the period that is needed by the series of capacitors for the purpose of having the voltage at their ends go from 1/3 to 2/3 of the power voltage (since the 555 timer is powered at 9V, the passage occurs between 3 and 6 volt, that respectively correspond to the voltage between pins 8 and 1) and at a low level (about zero volts) in the time passed from when the voltage at the ends of the capacitors – in the discharge phase – decreases from 2/3 of the power voltage to 1/3.

The times depend on the values of the R1, R2 and R3 resistors, and are more similar the more the sum R2+R3 is smaller with respect to R1: in fact the charging occurs through the three resistors while the discharging occurs only through R2 and R3.

Let’s see now the role played by the diode D1 that – when the capacitors are charging – bypasses R3 and the part of R2 that is inserted between the pointer and the end connected to R3; when the charging current of the capacitors is such to determine more than 0.6 V at the ends of such an equivalent resistance, the diode starts to conduct, so that the charging of C1 and C2 is carried out only through R1 and the part of R2 that is between the end connected to the latter and the pointer. When discharging, the diode is always interdicted. If we wanted to consider the D1 diode as an ideal one, we may add that it intervenes – when charging – by shortcircuiting the lower part of the R2 and R3 as well. Therefore, and by simplifying, it is possible to say that C1 and C2 are discharged through R3 and the lower part of the R2 potentiometer, while it is charged by means of R1 and of the upper part of R2.

This allows – in theory and within certain limits – to vary the duty-cycle of the rectangular wave, that is supplied by the pin 3, between 0 and 100%. This allows to keep the frequency of the said wave constant, as the position of the R2’s pointer changes.

Therefore, the duration of the output pulse at a high level is determined like this:

th = 0.693 (Ra+Rb) C

in which the presence of the diode D1 is neglected; C is the series of C1 and C2, that is equal to C1xC2/(C1+C2) and is worth, as we said before, 500 pF. Such a duration corresponds with the charging time of the capacitors.

On the other hand, the pause lasts for a time that is equal to:

tl = 0.693 x Rb x C

and corresponds to the discharging time of the capacitors in series.

The duration of the period T is equal to th + tl and the duty-cycle is worth:

dc = th/T

If the R2’s pointer is moved completely towards R1, Ra is worth R1 and Rb is equal to R2+R3 and is therefore 102 kohm; actually if we suppose that the diode D1 short circuits Rb, the duration of the pulse is equal to:

th = 0.693 (1 k) 500 pF = 0.3465 µs

The duration of the pause is instead worth:

tl = 0.693 x 101 kx 500 pF = 0.035 ms

In this case, the theoretical period is of about 0,353 ms and the duty-cycle is worth:

dc = 0.3465 µs/0.035 ms = 0.0099

that is to say, 0.99%.

In theory, the frequency is worth 28 kHz, even though – given that the diode intervenes on the conditions that have been previously explained – it is actually 25 kHz.

Let’s bring now the R2’s pointer completely towards R3; at this point, Ra is worth 101 kohm (R1+R2) and Rb is 1 kohm (R3). The duration of the pulse amounts to:

while the pause lasts:

tl = 0.693 x 1 k x 500 pF = 0.3465 µs

In this case the period lasts 0.03577 ms and the frequency is equal to 27.95 kHz, while the duty-cycle is worth:

dc = 0.03543 ms / 03577 ms = 0.99

therefore, that’s 99%.

Once the functioning of the 555 timer has been clarified, we may proceed with the analysis of the circuit, and see that the signal supplied by the OUT pin drives – by means of the resistive voltage divider that is composed of R4 and R5 – the T1 MOSFET’s gate; the latter is a N channel (enhancement mode) component that is used as a static switch, so to apply the pulses generated by the 555 timer – and power amplified – to the motor (connected between the + and – OUT contacts). The diode D2, that is connected in parallel to the output clamps, suppresses the inverse voltage pulses that are generated by the motor when the brushes commute on the collector and each possible inverse voltage peak deriving from the driving of inductive loads.

Let’s end this analysis of the circuit by talking about the power source, that is applied to the + and – PWR clamps and that reaches – in parallel – the input of the U2 regulator and the power circuit for the OUT output, opportunely filtered by the C5 electrolytic capacitor (whose purpose is the one to suppress the rectangular ripples of the voltage on the line when the MOSFET pulses on a motor that draws much current). The filtering that is carried out by the capacitor ensures that U2 is not disturbed and that it may obtain a clean and well stabilized 9 volt voltage at its output (OUT), a voltage that is needed in order for the functioning of the Pulse Width Modulator (based on the 555 timer); possible remains of the commutations that are found on the main power line and that have passed through the 7809 are lessened by the C4 electrolytic capacitor. The presence of the power source is signalled by the LD1 LED, that is protected by the current limiting resistor, R6.

TECHNICAL FEATURES

Power voltage: 12 ÷35Vcc

Motor voltage: 12÷35 Vcc

Motor current: 5 A

Max motor power: 200 W

PWM frequency: 25 kHz

Speed regulation: 0÷100%

From openstore

SPEED CONTROL FOR DC MOTOR TO 10-40V 5A